CTCSS encoder

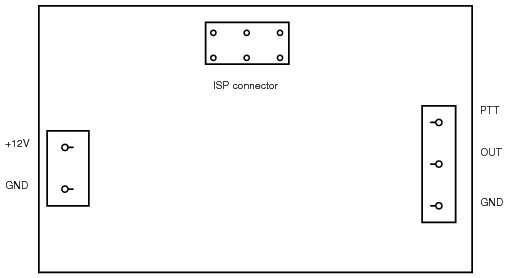

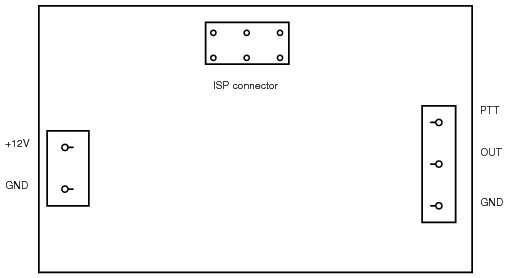

Connections

|

|

|

CTCSS encoder |

Connections |

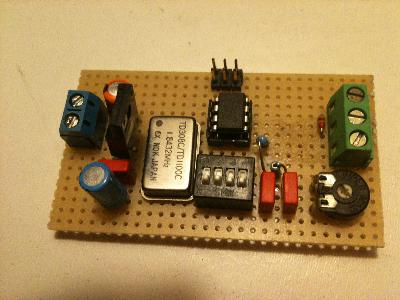

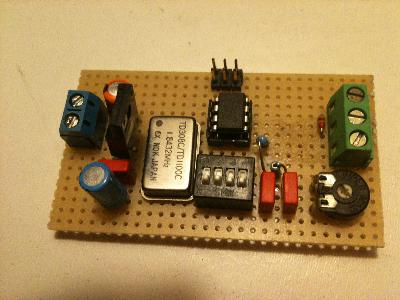

![[ctcss.png]](ctcss.png)

| S2 | S3 | Output |

| on | on | 71.9 Hz |

| on | off | 77.0 Hz |

| off | on | 82.5 Hz |

| off | off | 88.5 Hz |

| S1 | S2 | S3 | Output | S1 | S2 | S3 | Output | |

| on | on | on | 71.9 Hz | off | on | on | 67.0 Hz | |

| on | on | off | 77.0 Hz | off | on | off | 250.0 | |

| on | off | on | 82.5 Hz | off | off | on | 500.0 Hz | |

| on | off | off | 88.5 Hz | off | off | off | 1000.0 Hz |

|

|

|

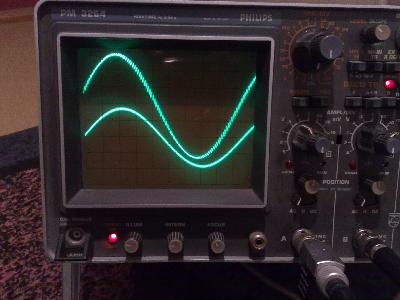

Upper trace: signal after 1st RC section Lower trace: signal after 2nd RC section Photo: PE1GGX |

Specification: 71.9 Hz +/- 0.4% ;-) Photo: PE1GGX |